開発事例

バーチャル ASSP ソリューション

ASSPと FPGA の間のコンセプト=vASSP

市販品のメリットと FPGA のメリットを融合したソリューション。

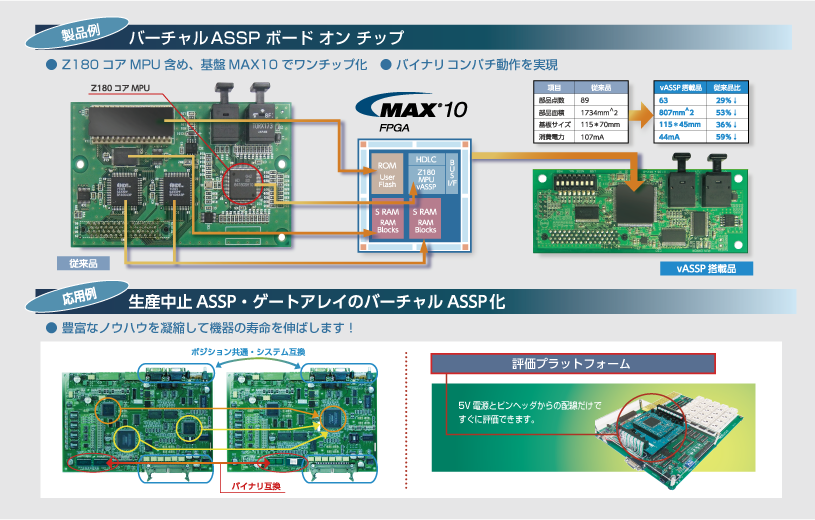

<製品例>

バーチャル ASSP ボード オン チップ

● Z180 コア MPU 含め、基盤 MAX10 でワンチップ化 ●バイナリコンパチ動作を実現

<応用例>

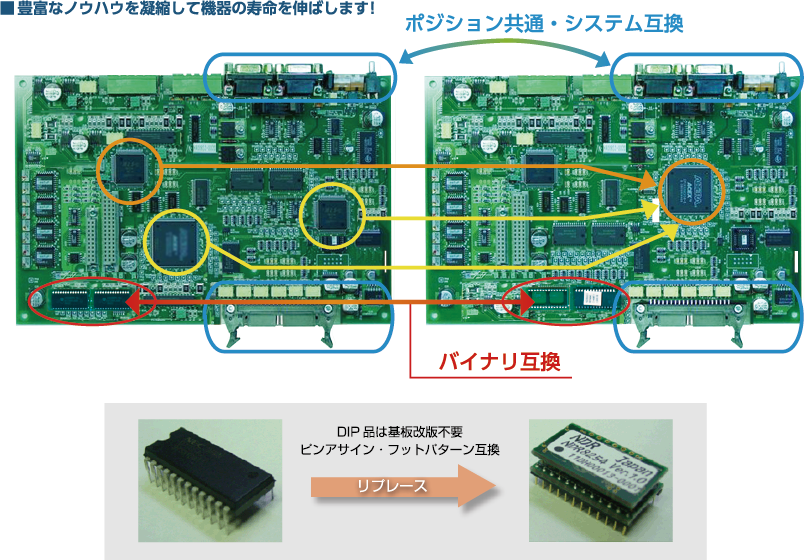

生産中止 ASSP・ゲートアレイのバーチャル ASSP 化

● ポジション共通・システム互換、バイナリ互換で機器の寿命を伸ばす

カテゴリー

生産中止デバイスを FPGA へリプレース

産業機器はユーザーの導入コスト、メーカーの開発コストが高価なことから長寿命が要求されますが、製品の保守において UART 等の ASSP や、開発した ASIC の生産中止が問題になります。

弊社では、生産中止になった ASSP、ASIC を FPGA にリプレースし製品寿命の延長に貢献しました。

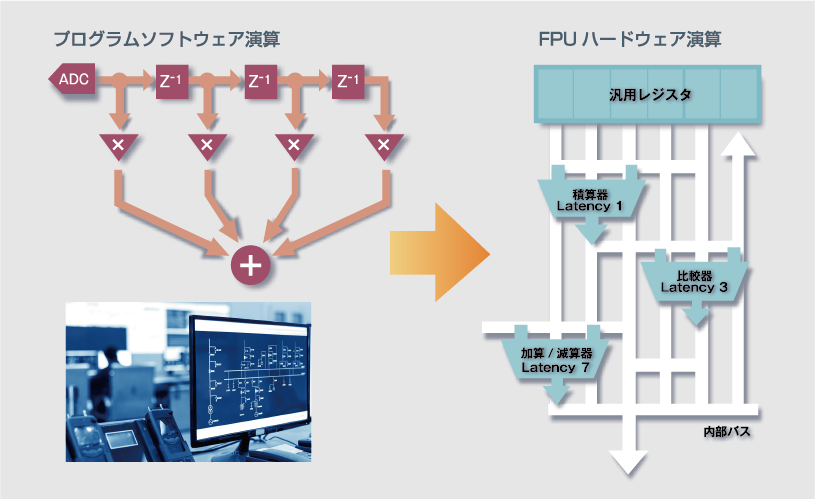

IEEE754 準拠 32bit 浮動小数点演算ユニット

浮動小数点 FIR 演算回路を FPGA で実装し高速演算を実現!

(IEEE 754 32bit に準拠した浮動小数点演算ユニットを搭載)

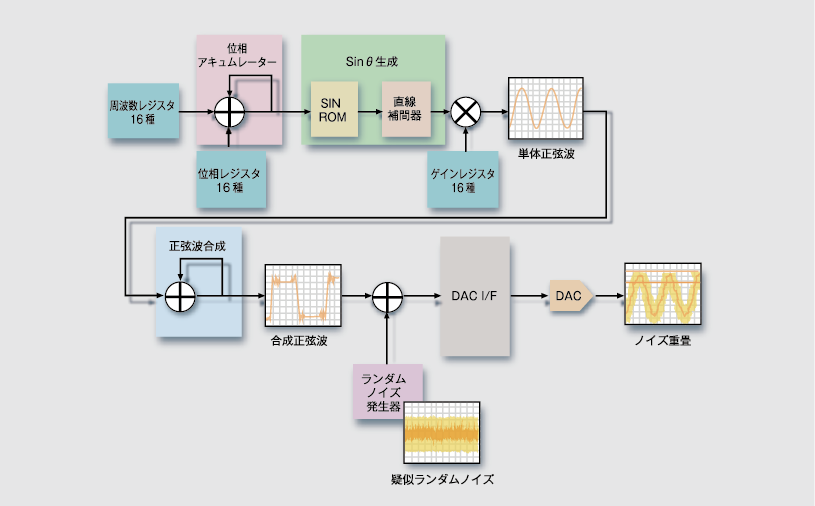

DDS FPGA 開発 (正弦波発生)

FPGA で任意周波数の正弦波を発生させ、お客様専用の DDS (ダイレクト・デジタル・シンセサイザ) を開発しました。

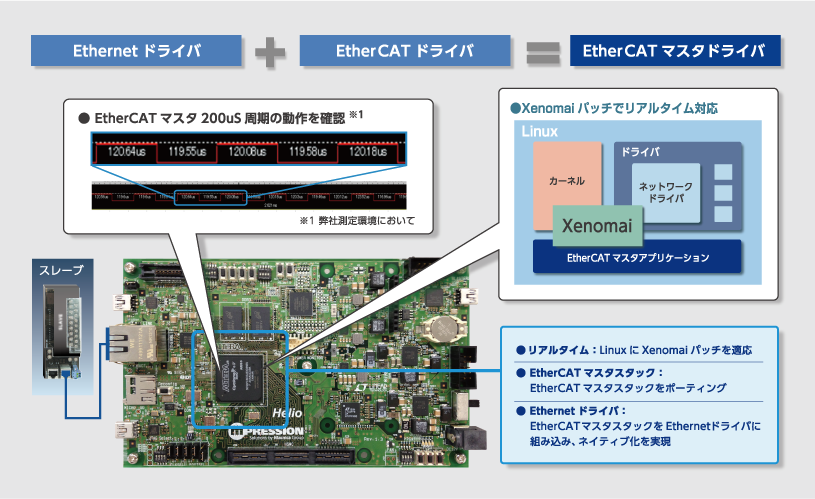

オープンソースでつくる EtherCAT マスタ

Xenomai パッチを適用し、リアルタイムに対応するオープンソースの EtherCAT マスタ環境を構築しました。

<特徴>

● リアルタイム:Linux に Xenomai パッチを適用

● EtherCAT マスタスタック:EtherCAT マスタスタックをポーティング

● Ethernet ドライバ:EtherCAT マスタスタックをEthernetドライバに組込み、ネイティブ化を実現

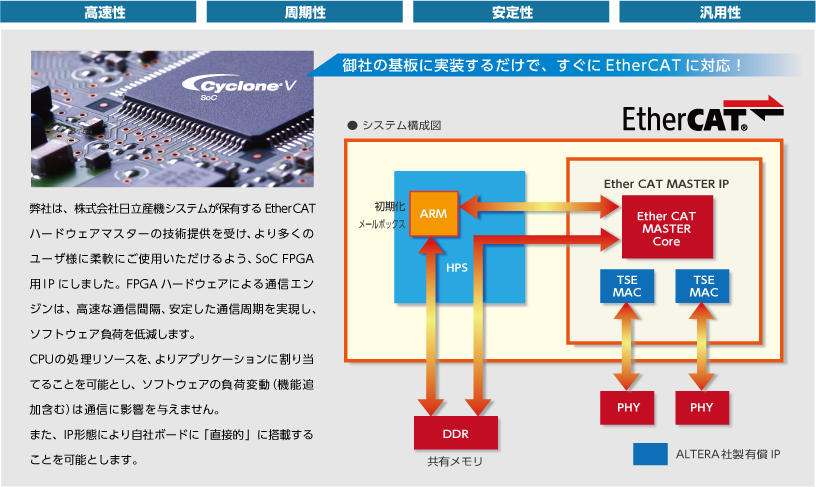

ハードウェア EtherCAT マスタ IP

日本発、ソフトウェア負荷を大幅に低減する高性能 SoC FPGA 用 IP が誕生しました。

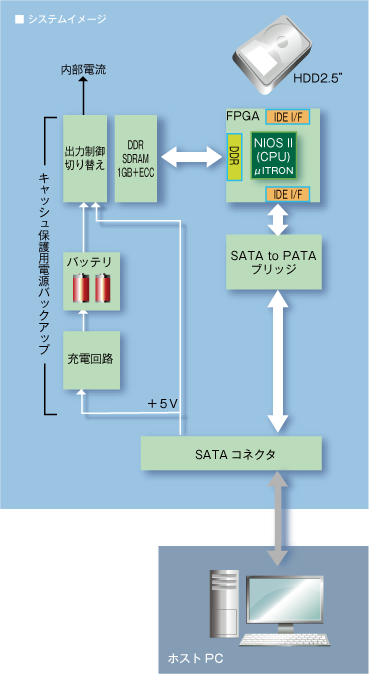

HDD アクセラレーター

2.5インチ HDD のフロントエンドに 1GB のキャッシュを搭載し、IOPS/スループットを向上させる HDD アクセラレータボード。

カテゴリー

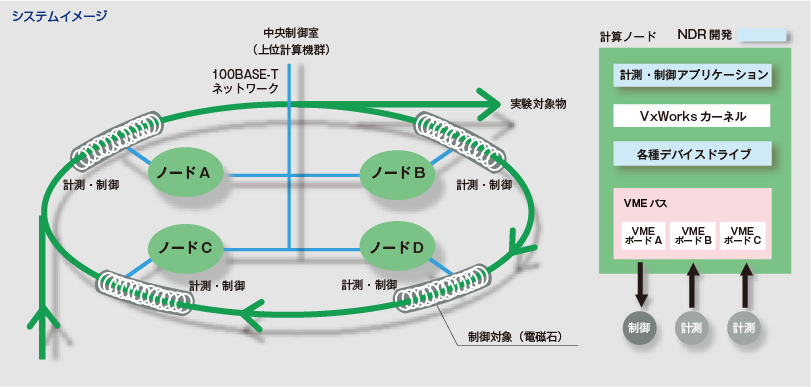

加速器の電磁石ノード

ネットワークを介して、中央制御室より制御指令を受け、電磁石電源コントローラへの出力パターン制御と出力波形および各機器状態のモニタを行うシステムを開発しました。

技術関連

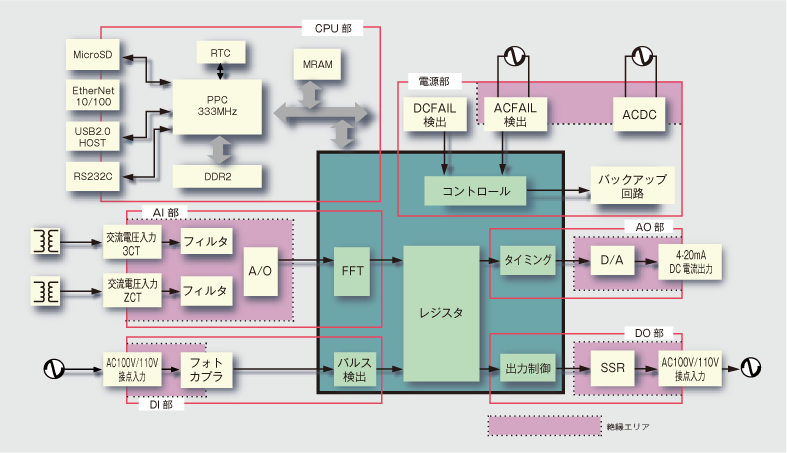

EtherNet/IP 機能拡張による高機能 PLC ユニットの開発

産業用 CPU ユニットで EtherNet/IP を使用したデータ共有分散処理システムをハードウェア・ソフトウェア一括で開発しました。

カテゴリー

技術関連